| To Home |

|||

| 亀DAS-703ES丒僨僕僞儖夞楬晹偺夝愢亁丂丂丂乮DAS-703ES偺僒乕價僗儅僯儏傾儖傛傝敳悎宖嵹乯

|

|||

| 仭DAI乮Digital Audio Interface)偺揱憲曽幃仭 | |||

|

|||

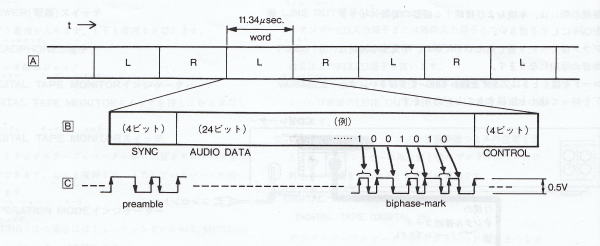

| 忋恾偼僨僕僞儖僆乕僨傿僆怣崋偺揱憲曽幃傪帵偟偰偄傞丅僨僕僞儖丒僆乕僨傿僆丒僀儞僞乕僼僃乕僗乮DAI乯偱偼丄1杮偺僨僕僞儖働乕僽儖偱L ch丄R

ch偺2偮偺僨乕僞傪揱憲偡傞丅偙偺偨傔丄恾A偺傛偆偵丄L ch僨乕僞偲R ch僨乕僞傪岎屳偵憲庴怣偡傞丄帪娫暘妱懡廳揱憲曽幃傪梡偄傞丅僒儞僾儕儞僌廃攇悢偑44.1倠Hz偺応崌乮CD)丄L

ch偲R ch偦傟偧傟偺僨乕僞偼1昩娫偵44,100屄偢偮丄椉僠儍儞僱儖崌傢偣偰88,200屄揱憲偝傟傞丅傂偲偮偺僠儍儞僱儖僨乕僞嬫娫乮Word)偺挿偝偼11.34兪sec偱偁傞丅 傂偲偮偺儚乕僪偼32價僢僩偱峔惉偝傟偰偄傞丅價僢僩偺嬫暘偗偼恾B偵帵偡偲偍傝偱偁傞丅 仭嵟弶偺4價僢僩偼摨婜傪偲傞偨傔偺SYNC乮僔儞僋乯晹暘偱丄屻弎偺僾儕傾儞僽儖偑偼傔崬傑傟偰偄傞丅 仭師偼僆乕僨傿僆僨乕僞偑擖傞晹暘偱丄24價僢僩偺僼傿乕儖僪偑偁傞丅偨偩偟CD偺傛偆偵僆乕僨傿僆僨乕僞偲偟偰偼16價僢僩偺傕偺偑懡偔丄偆偟傠偐傜16價僢僩偺傒傪巊梡偟偰偄傞丅 仭嵟屻偺4價僢僩偼丄僄儞僼傽僔僗偺ON/OFF傗僒僽僐乕僪側偳丄僨乕僞偵晅悘偟偨忣曬傪偺偣傞僐儞僩儘乕儖晹暘偱偁傞丅 偙偺傛偆偵慻傒棫偰傜傟偨僨乕僞乕偵偼丄恾C偵帵偡傛偆偵僨乕僞侽偵侾夞揮丄僨乕僞侾偵俀夞揮傪懳墳偝偣偨丄僶僀僼僃乕僘儅乕僋乮biphase mark乯偲屇偽傟傞曄挷偑偐偗傜傟傞丅偨偩偟丄CYNC晹暘偼椺奜偱丄僾儕傾儞僽儖乮preamble乯偲屇偽傟傞摿庩側僷僞乕儞偑偼傔崬傑傟偰偄傞丅 僾儕傾儞僽儖偱偼僨乕僞偵傛傞斀揮墳摎偑柍帇偝傟偰偍傝丄僴僀儗儀儖偑懕偔帪娫偑偳偺晹暘傛傝傕挿偔側偭偰偄傞丅庴怣懁偱偁傞D/A僐儞僶乕僞乕擖椡晹偱偼僾儕傾儞僽儖晹傪巊偭偰摨婜傪偲傞丅 恾C偺攇宍偼丄僀儞僺乕僟儞僗俈俆兌偺摨幉働乕僽儖拞傪侽丏俆V倫亅倫偺儗儀儖偱揱憲偝傟丄婡婍偲偺愙懕偼RCA僺儞働乕僽儖傪巊梡偟偰偄傞丅 |

|||

| 丂 | |||

| 侾丂僨僕僞儖晹 | |||

| DAS-703ES偺僨僕僞儖宯偼丄DAI僼僅乕儅僢僩偱憲傜傟偰棃偨怣崋偐傜僨乕僞傪拪弌偟丄僨僕僞儖僼傿儖僞乕偱僒儞僾儖儗乕僩曄姺乮俀攞乯偟丄D/A曄姺IC偵傛傝丄傾僫儘僌怣崋偵曄姺偝傟傞丅 杮婡撪偱偼帺恎偱悈徎敪怳婍偼帩偨偢丄偡傋偰偺僋儘僢僋丒僞僀儈儞僌偼擖椡偝傟偨怣崋偐傜PLL偵傛傝摼偰偄傞丅PLL偼俀屄偁傝偦傟偧傟RX PLL丄APL PLL偲屇傫偱偄傞丅偙偺PLL偺暿摍偐傜杮婡偺僨僕僞儖宯偼戝偒偔俆偮偺宯摑偵暘偗傜傟傞丅 |

|||

| 丂 | |||

| 侾亅侾丂RX AMP宯 | |||

| 擖椡怣崋乮侽丏俆V倫亅倫乯傪儘僕僢僋儗儀儖乮係V倫亅倫掱搙乯傑偱憹暆偡傞偲嫟偵丄僄僢僕専弌偲扨埨掕儅儖僠偵傛傝擖椡怣崋偐傜摨婜怣崋俀FSR傪惗惉偡傞丅俀SFR偼俀屄偺PLL偺栚昗偲偟偰巊傢傟傞丅 傑偨杮婡偵偼丄擖椡俀宯摑偲僨僕僞儖丒僥乕僾丒儌僯僞乕夞楬偑愝偗傜傟偰偄傞丅僨僕僞儖丒僥乕僾丒儌僯僞乕夞楬偱偼丄DIGITAL REC OUT抂巕偵丄擖椡愗姺偱慖戰偝傟偨擖椡怣崋偑忢偵弌椡偝傟傞丅僨僕僞儖丒僥乕僾丒儌僯僞乕SW偑ON偺帪偼丄擖椡偲偟偰DIGITAL TAPE IN偑慖戰偝傟傞丅 丂 |

|||

| 侾亅俀丂RX宯乮RX PLL偵廬懏乯 | |||

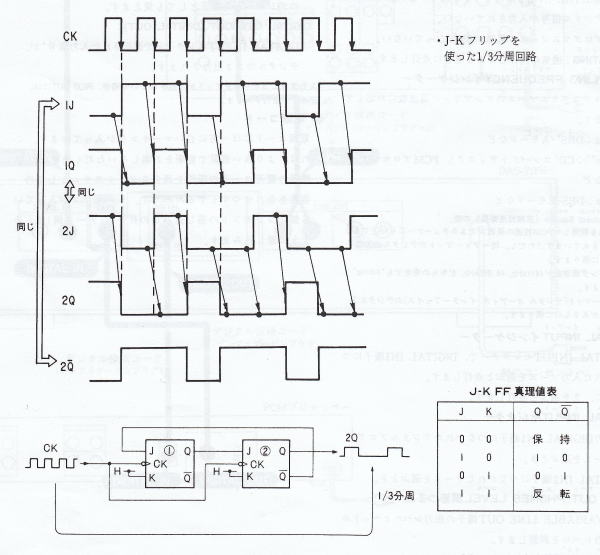

| DAI僼僅乕儅僢僩僨僐乕僪梡IC CX23053(IC706)偲丄僨僕僞儖僼傿儖僞乕CX23034(IC708)丄媦傃偦傟傜偺僋儘僢僋傪敪惗偝偣傞RX

PLL偱峔惉偝傟偰偄傞丅 CX23053梡偺僋儘僢僋偼256倖倱丄CX23034梡偺僋儘僢僋偼384倖倱偱偁傞丅偦偙偱丄RX PLL偺VCO敪怳廃攇悢偼384倖倱偲偟偰偄傞丅偙傟傪74HC112乮IC712乯偱1/3暘廃偟偨屻丄峏偵74HC393乮IC713乯偱1/128暘廃偟丄2FSR偲埵憡斾妑傪偡傞丅 256倖倱偼丄384倖倱傪1/3暘廃偟偨屻偺128倖倱傪俀掽攞偡傞偙偲偱摼偰偄傞丅IC712偱峴偭偰偄傞僞僀儈儞僌僠儍乕僩傪埲壓偵帵偡丅 |

|||

丂 仭IC712乮74HC112)偺僞僀儈儞僌僠儍乕僩仭 丂 |

|||

|

|||

| DIA怣崋RX偼丄堦搙D儔僢僠乮IC704乯偱僞僀儈儞僌曗惓偟偰偐傜CX23053偵擖椡偝傟傞丅CX23503偺弌椡偼丄LR岎屳價僢僩僔儕傾儖偺DATA偲丄偦偺僞僀儈儞僌寛掕梡偺BCK丄LRCK丄偺俁幰偱偁傞丅偙傟傜偺偆偪LRCK偼斀揮傪偲偭偰丄懠偼偦偺傑傑僨僕僞儖僼傿儖僞乕CX23034傊憲傜傟傞丅 CD僾儗乕儎乕偺怣崋張棟偱偼BCK偑49倖倱乮戞堦悽戙CX7935乯傗丄48倖倱乮戞擇悽戙CX2305乯偵側偭偰偍傝DATA偵偡偒娫偑偁偭偨偑丄CX23053偺弌椡DATA偼儀僞媗傔偱BCK偼32倖倱偱偁傞丅 僨僕僞儖僼傿儖僞乕偱偼僒儞僾儕儞僌儗乕僩偑俀攞偵曄姺偝傟偰偄傞丅乮僨僕僞儖僼傿儖僞乕偐傜弌椡偝傟傞僨乕僞偺僒儞僾儕儞僌廃攇悢傪倖倓倱偲偡傞偲倖倓倱亖俀倖倱偲偄偆偙偲偵側傞乯僨乕僞偼18價僢僩暘弌椡偝傟偰偄偰丄僨乕僞乕偲僨乕僞偺娫偵偼丄6價僢僩偺偡偒娫偑偁傞丅 價僢僩僋儘僢僋BCK偼僨乕僞偵懳墳偟偰18亄6亖24僷儖僗偱侾僒儞僾儖暘丄L ch丄R ch偱48僷儖僗乮48倖倱乯弌椡偝傟偰偍傝丄傕偲偺倖倱偵懳偟偰96倖倱偺儗乕僩偲側傞丅 LCK偼僨乕僞偺16價僢僩栚偵僄僢僕偑偁傝丄偙偺棫偪忋偑傝偑僔儕僷儔曄姺偺僞僀儈儞僌偲側傞丅 |

|||

| 丂 | |||

| 侾亅俁丂D/A宯 | |||

| 僨僕僞儖僼傿儖僞乕CX23034乮IC708乯偐傜弌椡偝傟偨DATA偼丄僼僅僩僇僢僾儔乕PC910傪捠夁屻丄僔僼僩儗僕僗僞CDX1058Q乮IC505乯偵擖椡偝傟僔儕僷儔曄姺偝傟傞丅 D/A曄姺偺拞怱偼PCM53JG-1乮IC507丄IC607乯偵丄僷儔儗儖僨乕僞偺擖椡偱捈偪偵偙傟偵懳墳偟偨傾僫儘僌揹棳傪弌椡偡傞丅偮傑傝丄僷儔儗儖弌椡偼D/A曄姺偺僗僞乕僩傪堄枴偡傞丅僷儔儗儖僨乕僞偼LRCK偺棫偪忋偑傝僄僢僕偱弌椡偝傟傞丅IC507丄IC607偺弌椡揹棳偼僒儞僾儖仌儂乕儖僪傊憲傜傟傞丅 |

|||

| 丂 | |||

| 侾亅係丂APT宯乮APT PLL偵廬懏乯 | |||

| 僒儞僾儖仌儂乕儖僪偺APT丄APT-H傪嶌傝弌偡丅APT PLL偺VCO偼僔乕儖僪働乕僗偵廂傔傜傟偰偄傞VCO僽儘僢僋偱偁傞丅敪怳廃攇悢偼256倖倱丅偙傟傪74HC393乮IC716乯偱1/8丄1/32丄1/64丄1/128暘廃偟偰丄A32FS丄A8FS丄A4FS丄A2FS傪嶌傝弌偡丅偙偺4怣崋偲D儔僢僠傪慻傒崌傢偣偰APT丄APT-H傪摼傞丅 APT PLL偼儘僢僋偡傞棫偪忋偑傝帪娫偑抶偄偨傔丄擖椡愗傝姺偊捈屻偺傛偆偵堦搙擖椡怣崋RX偑搑愗傟偨屻栺係昩娫偼RX PLL偐傜怣崋傪傕傜偭偰APT丄APT-H傪嶌偭偰偄傞丅 |

|||

| 丂 | |||

| 侾亅俆丂僐儞僩儘乕儖宯 | |||

| 僒儞僾儕儞僌廃攇悢倖倱偺昞帵丄倖倱偺愗傝姺偊丄僆儁儗乕僔儑儞儌乕僪乮儈儏乕僥傿儞僌乯摍丄捠忢儅僀僐儞偱峴偆傛偆側摦嶌傪杮婡偱偼僴乕僪儘僕僢僋偱峴偭偰偄傞丅 戙昞揑偱廳梫側偺偼師偺偲偍傝丅 |

|||

| 侾乯俀倖倱嵞惗夞楬 | |||

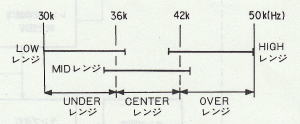

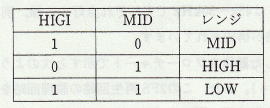

| 扨埨掕儅儖僠傪梡偄偨俀FS嵞惗夞楬偱偼嵞惗壜擻側僒儞僾儕儞僌廃攇悢偑丄偦偺忋尷偲壓尷偱1.35攞掱搙偱偁傞丅偦偙偱杮婡偱偼30倠乣50倠Hz偺僒儞僾儕儞僌廃攇悢偱埨掕偟偨俀FS嵞惗傪壜擻偲偡傞偨傔丄扨埨掕儅儖僠偺帪掕悢傪俁偮偵愗傝姺偊偰偄傞丅 偙偺愗傝姺偊偵懳墳偟偰俁偮偺嵞惗儗儞僕偑師偵帵偡條偵愝掕偝傟偰偄傞乮塃恾乯丅偝傜偵嵞惗儗儞僕偑僆乕僶乕儔僢僾偡傞僒儞僾儕儞僌廃攇悢偵懳偟偰傕丄傛傝埨掕側曽偺儗儞僕偱俀FS嵞惗傪峴傢偣傞傛偆偵側偭偰偄傞丅 |

|

| 偡側傢偪 嘆MID儗儞僕偱俀FS嵞惗偑峴傢傟偰偄傞偵傕偐偐傢傜偢丄僒儞僾儕儞僌廃攇悢偼UNDER儗儞僕偁傞偄偼OVER儗儞僕偺応崌丅 嘇LOW儗儞僕傑偨偼HIGH儗儞僕偵偍偄偰俀FS嵞惗偟偰偄傞偑僒儞僾儕儞僌廃攇悢偼CENTER儗儞僕偺応崌丅 |

|||

| 丂 | |||

| 丂 仭俀FS嵞惗夞楬僽儘僢僋僟僀傾僌儔儉仭 |

|||

丂 |

|||

| 丂 | |||

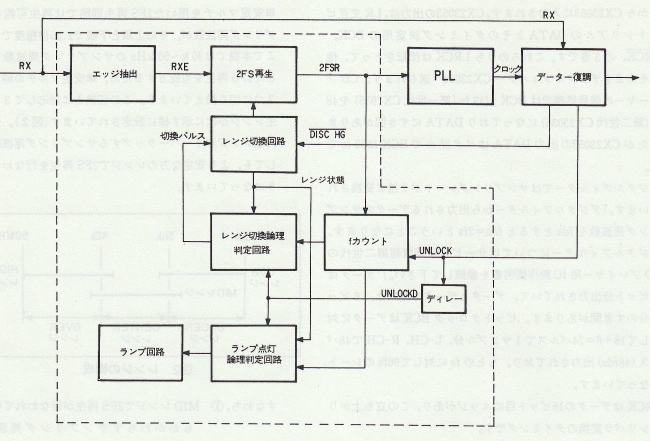

| 忋恾偵2FS嵞惗夞楬偺僽儘僢僋僟僀傾僌儔儉傪帵偡丅俀FS嵞惗夞楬帺懱偼RX宯偺夞楬偱偁傞偑丄3儗儞僕廃攇悢偵墳偠偰愗傝姺偊傞夞楬偑峏偵昁梫偱偁傞丅師偵偙偺愗傝姺偊夞楬偺摦嶌傪愢柧偡傞丅 丂 |

|||

| PLL偑儘僢僋偟偰偄側偄忬懺偱偼丄僨乕僞暅挷偵傛傝DISCHG-H怣崋偑弌傞丅偙傟偵傛傝3儗儞僕H仺M仺L仺H偺弴偵愗傝姺偊偰備偔丅僠僃僢僇乕丒儔儞僪偺HIGH-H偲MID-H偵傛傝塃昞偺傛偆側儗儞僕偵側傞丅 |  |

||

| PLL偑儘僢僋偟偨屻偼 嘆PLL偑儘僢僋偟偨偙偲偵傛傝丄UNLOCK怣崋偼High仺Low偲曄壔偡傞丅 嘇偙偺僱僈僄僢僕偵傛傝廃攇悢偺僇僂儞僩傪奐巒偡傞丅 嘊僇僂儞僞乕偺寢壥偲愗姺夞楬偵傛傝丄弌椡偝傟傞儗儞僕偺忬懺忣曬偵傛傝榑棟敾掕傪峴偄丄慜弎偺儗儞僕偺曄峏傪梫偡傞応崌偼儗儞僕愗姺僷儖僗傪敪惗偝偣傞偲摨帪偵堦搙儘僢僋傪偼偢偡丅 嘋偙偺儗儞僕愗姺僷儖僗偺敪惗偼UNLOCK傪僨傿儗乕偝偣偨UNLOCKD偺僱僈僄僢僕偺僞僀儈儞僌偱峴偆丅 嘍揔愗側儗儞僕偱儘僢僋偡傞傑偱嘆乣嘋傪孞傝曉偡丅 嘐儔儞僾偺揰摂偼H丄M丄L儗儞僕偲偼懡彮堎側傞丅偡側傢偪丄32倠偼30倠乣36倠Hz丄44倠偼36倠乣45倠Hz丄48倠偼45倠乣50倠Hz偱偦傟偧傟揰摂偡傞傛偆丄暿偺榑棟夞楬偑峔惉偝傟偰偄傞丅 |

|||

| 俀乯UNLOCK-H丂ULLD | |||

| UNLOCK偲揹尮ON捈屻偺RST偲偺OR傪偲偭偨怣崋偑MUTH偲屇偽傟傞怣崋偱偁傞丅偙偺MUTH傪棫壓傝偺傒3 倣sec僨傿儗乕偝偣偨怣崋偑UNLOCK-H偱偁傞丅偙傟偑Low偵側傞偲僷儔儗儖僨乕僞偑僋儕傾偝傟僨僕僞儖儈儏乕僩忬懺偲側傝丄摨帪偵僆乕僨傿僆儈儏乕僩傕偐偐傞丅 UNLOCK偑OFF偟偰偐傜UNLOCK-H偑High偵側傞傑偱栺3 msec偺娫偵偼僨僕僞儖僼傿儖僞乕偺儕僼儗僢僔儏乮柍岠僨乕僞偺塭嬁偑側偔側傞乯偑峴傢傟傞丅 ULLD偼丄MUTH偺棫偪忋偑傝傪栺4昩僨傿儗乕偟偨怣崋偱APT丄APT-H偺惗惉尮傪RX PLL偐傜APT PLL傊愗傝姺偊傞偨傔偺怣崋偱偁傞丅 |

|||

| 丂 | |||

| 俁乯CS | |||

| CX23053偺僔僗僥儉儕僙僢僩梡僞僀儈儞僌尮偱僞僀儅乕IC 555D偵傛傝摼偰偄傞丅 | |||

| 丂 | |||

| 係乯EMP | |||

| EMP偼僨僕僞儖僜乕僗偵僄儞僼傽僔僗偑偐偐偭偰偄傞帪丄CX23053傛傝弌椡偝傟傞怣崋偱偁傞丅 | |||

| 丂 | |||

|

|

|||

| 忋婰偼DAS-703ES偺僨僕僞儖夞楬晹偺摦嶌愢柧偱偁傞丅側偍杮暥偼DAS-703ES偺僒乕價僗儅僯儏傾儖偐傜敳悎偟偰宖嵹偟偰偄傞丅 | |||

|

|

|||

| Copyright(c) 2008-2015 Masataka Ohnishi All Right Reserved |